开发语言

arcgis

node.js

npm

测试工程师

jmeter

语音

就业管理系统

类型转换

rtmp

OData

cve-2022-21449

互联网

微信小程序登录

爬山算法

湖南大学

次世代建模

k8s

运维开发

RSS

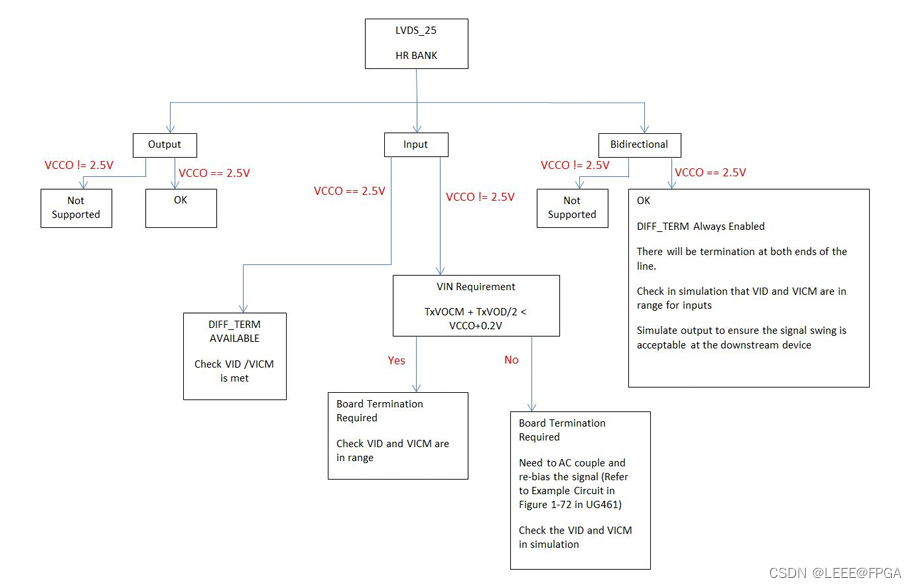

Lvds

2024/4/12 19:10:35异构集成的高速总线核算实例

带宽增长的问题

Shannon-Hartley定理给出了一个无线信道能够传输的信息总量 C BW log2(1SNR) 其中C为信道容量,BW为信号带宽,SNR为信道的信噪比,信息容量直接与信道带宽成正比。而信道带宽则直接由采样速率所确定。…

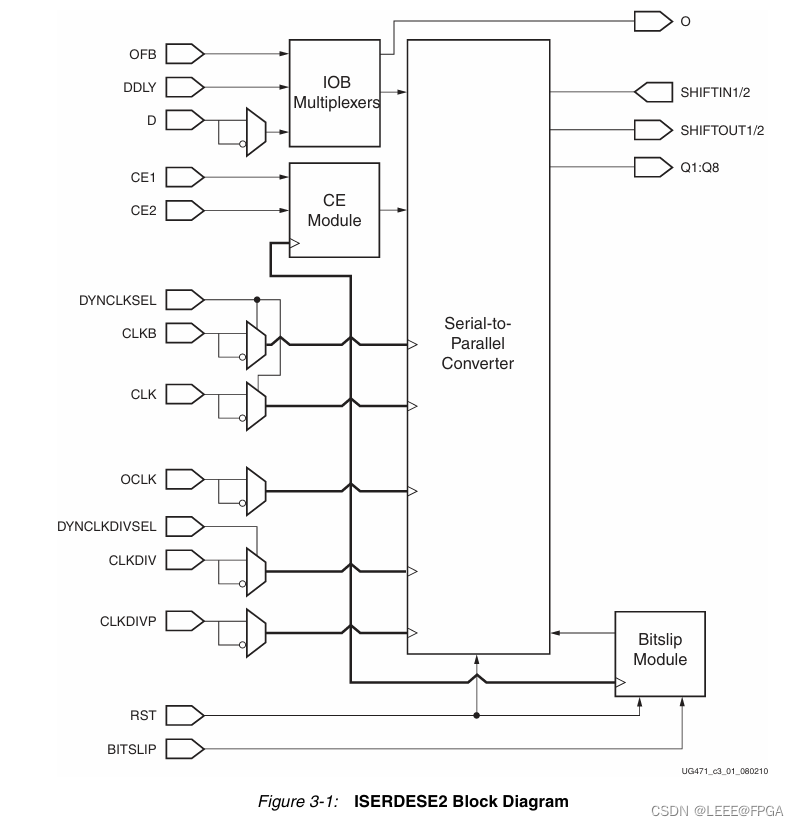

Xilinx LVDS ISERDESE2

ISERDESE2 7 系列 FPGA 是一款专用的串行到并行转换器,具有特定的时钟和逻辑功能,旨在促进高速源同步应用的实现。该ISERDESE2避免了在FPGA架构中设计解串器时遇到的额外时序复杂性.

ISERDESE2功能包括: 1,专用解串器/串行转换器 ISERDESE2解串器可实现高速数据传输,而无需…

基于FPGA的LVDS接口设计

实验内容:

通过LVDS接口,完成数据的收发测试。 上周居然开启了咸鱼模式,检讨一下 || 前集回顾:

《Xilinx - UG471中文翻译》(1)IDELAYE2原语介绍

《Xilinx - UG471中文翻译》(2)…

I/O接口标准(2):CML、PECL、LVECL和LVDS

2.差分信号接口标准 CML(Current-mode llogic)它并没有一个标准,是基于简单的差分放大器,如图2所示。通常取R1R250欧姆,|VOUT - VOUT-| R1 * i1 50*i1,不同的厂家i1值…

汽车IVI中控开发入门及进阶(九):显示屏

前言:

显示屏Display panel和触控屏Touch panel,可以说随着汽车四化的进展,屏越来越多,越来越大,越来越高清,成为IVI中控、智能座舱系统的重要组成部分。比如如下一个电阻触摸屏。 正文:

显示屏

主要功能就是显示,车载内容和信息的传递全靠显示屏,目前车载显示屏的…

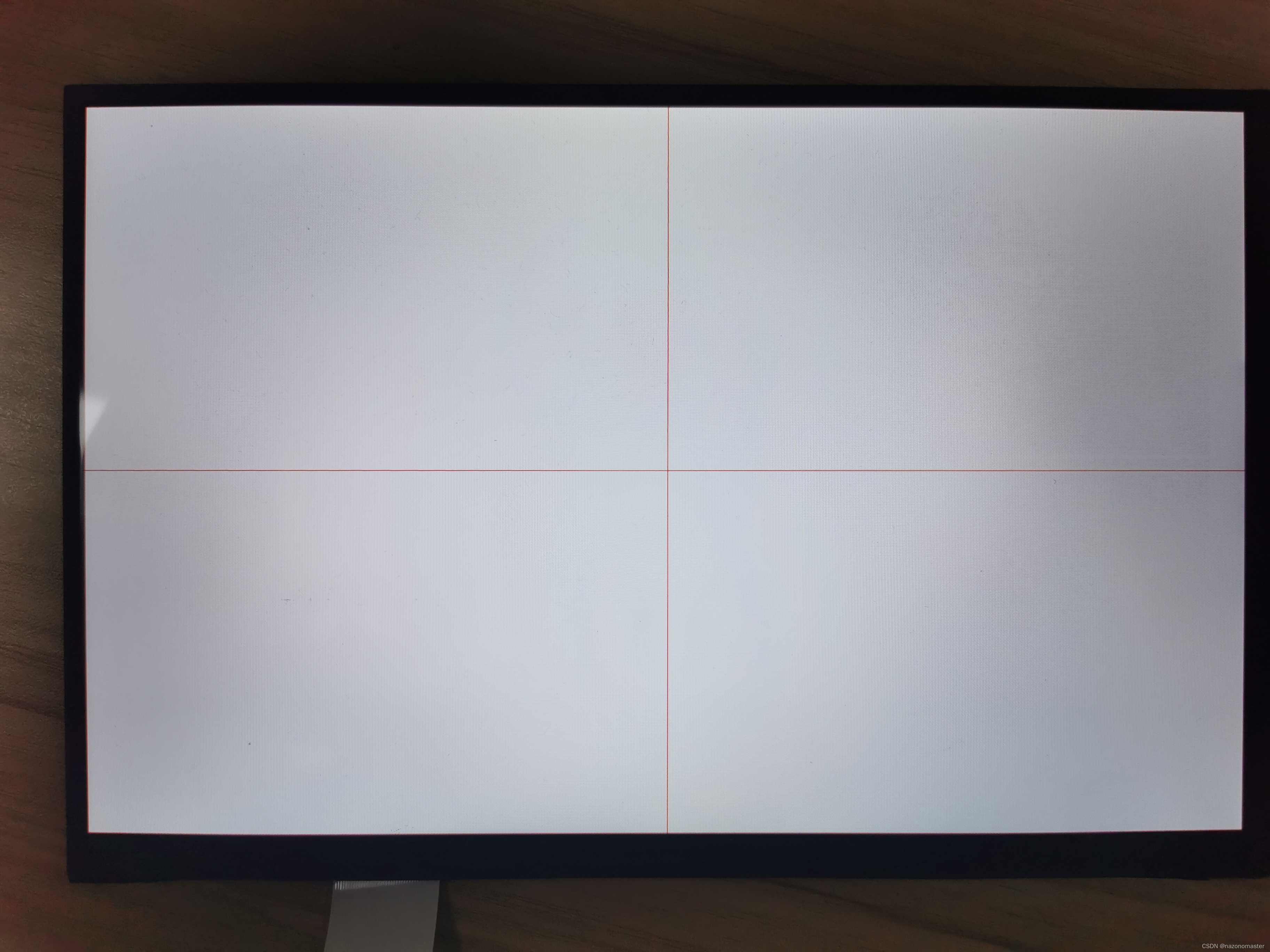

OpenHarmony4.0适配LVDS屏幕驱动

1.概述

手头有一块RK3568的开发板OK3568-C,但是还没有适配OpenHarmony,用的还是LVDS屏幕,但是官方和网上好像还没有OpenHarmony4.0的LVDS屏幕驱动的通用实现,所以决定尝试了一下适配该开发板,完成LVDS屏幕驱动的适配&…

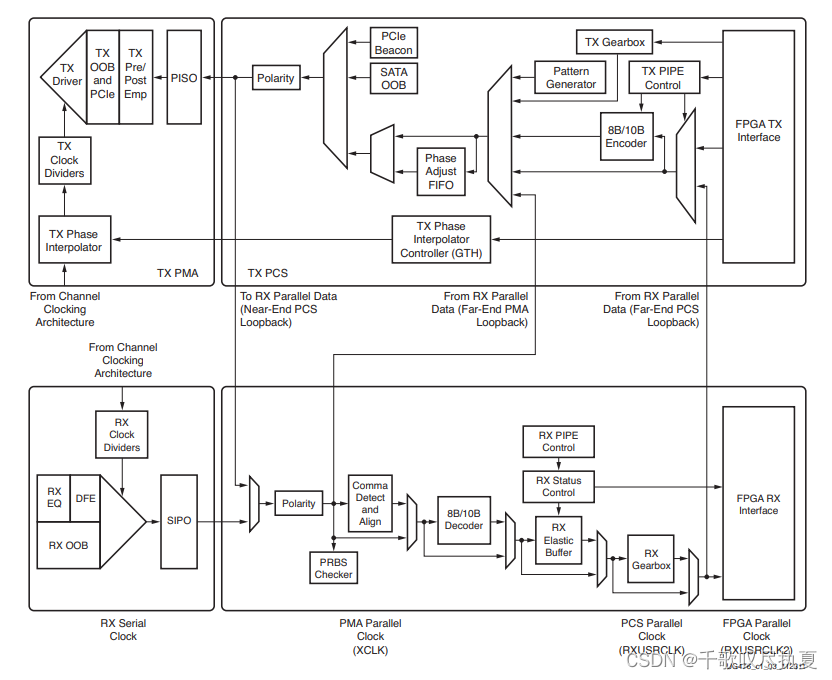

高速Serdes技术(FPGA领域应用)

目录引入一、Serdes(概念-历程)1、概念2、技术现状3、发展历程二、Serdes结构三、在FPGA领域中的运用四、Serdes跟Lvds的关系五、Xilinx 有关 serdes的文档六、参考文献引入 回顾接口技术发展历史,其实数据的传输最开始是低速的串行接口&…

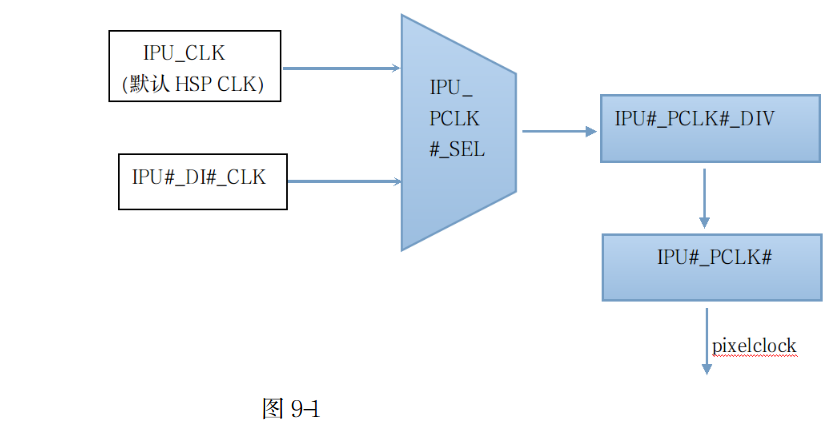

IMX6DL Lvds pixelclock 深入详解

写在前面的话: 嵌入式系统中有两个比较难搞的问题, 一个是电源,一个是Clock。随着现在电源管理芯片的成熟,我们将会越来越少地关注到电源的配置和设定(但管理应用还是比较广泛的)。 Clock系统是一个嵌…

CameraLink传输协议

一、CameraLink协议是一种专门针对机器视觉应用领域的串行通信协议,它使用低压差分信号(LVDS)进行数据的传输和通信。CameraLink标准是在ChannelLink标准的基础上多加了6对差分信号线,其中4对用于并行传输相机控制信号,另外2对用于相机和图像…

FPGA输出lvds信号点亮液晶屏

1 概述 该方案用于生成RGB信号,通过lvds接口驱动逻辑输出,点亮并驱动BP101WX-206液晶屏幕。 参考:下面为参考文章,内容非常详细。Xilinx LVDS Output——原语调用_vivado原语_ShareWow丶的博客http://t.csdn.cn/Zy37p 2 功能描述 …

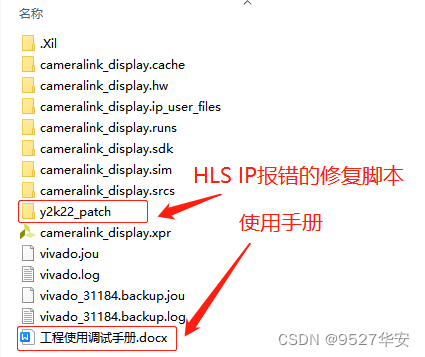

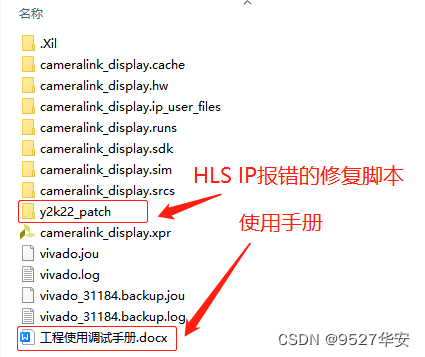

FPGA纯verilog实现CameraLink视频接收和发送,附带工程源码和技术支持

目录 1、前言2、CameraLink协议基础3、目前我已有的CameraLink收发工程4、设计方案5、CameraLink解码模块详解6、CameraLink编码模块详解7、vivado工程详解8、上板调试验证9、福利:工程代码的获取 1、前言

FPGA实现CameraLink视频编解码目前有两种方案:…

RGMII回环:IDDR+ODDR+差分接口

目录 一、实验内容二、原理解释三、程序1、顶层文件:2、子模块2.1 oddr模块2.2、iddr顶层模块2.3、iddr子模块 3、仿真4、注意5、下载工程及仿真 一、实验内容

1、通过IDDR和ODDR的方式完成RGMII协议; 2、外部接口使用OBUFDS、IBUFDS转换成差分接口&…

FPGA 高速接口(LVDS)

差分信号环路测试

1 概述

LVDS(Low Voltage Differential Signalin)是一种低振幅差分信号技术。它使用幅度非常低的信号(约350mV)通过一对差分PCB走线或平衡电缆传输数据。大部分高速数据传输中,都会用到LVDS传输。 …

FPGA实现HDMI转LVDS视频输出,纯verilog代码驱动,提供4套工程源码和技术支持

目录 1、前言免责声明 2、目前我这里已有的图像处理方案3、本 LVDS 方案的特点4、详细设计方案设计原理框图视频源选择静态彩条IT6802解码芯片配置及采集ADV7611解码芯片配置及采集silicon9011解码芯片配置及采集纯verilog的HDMI 解码模块奇偶场分离并串转换LVDS驱动 5、vivado…

FPGA采集CameraLink相机Base模式解码输出,附带工程源码和技术支持

目录 1、前言2、CameraLink协议基础3、目前我已有的CameraLink收发工程4、设计方案输入CameraLink相机LVDS视频解码视频缓存视频输出软件配置 5、vivado工程详解6、上板调试验证7、福利:工程代码的获取 1、前言

FPGA实现CameraLink视频编解码目前有两种方案&#x…

FPGA采集CameraLink相机Full模式解码输出,附带工程源码和技术支持

目录 1、前言2、CameraLink协议基础3、目前我已有的CameraLink收发工程4、设计方案输入CameraLink相机视频缓存视频输出软件配置 5、vivado工程详解6、上板调试验证7、福利:工程代码的获取 1、前言

FPGA实现CameraLink视频编解码目前有两种方案: 一是使…